Fuente: http://web.engr.oregonstate.edu/~moon/engr203/read/read3.pdf

Do you ever wonder how the processor in your computer was actually fabricated? How is it that engineers can put hundreds of millions of transistors into one device that measures only a few centimeters on a side (and with so few errors) so the devices actually function as expected?

Devices such as modern computer processors and semiconductor memories fall into a class known as integrated circuits (IC). They are so named because all of the components in the circuit (and their “wires”) are fabricated simultaneously onto a circuit during the manufacturing process. This is in contrast to circuits where each component is fabricated separately and then soldered or wired together onto a common board (such as those you probably build in your lab classes). Integrated circuits were first demonstrated independently by Jack Kilby at Texas Instruments and Robert Noyce at Fairchild Semiconductor in the late 1950s. Once developed, the ability to manufacture components

and their connections in parallel with good quality control meant that circuits with thousands (then millions, then billions) of components could be designed and built reliably.

Semiconductor Processing Basics

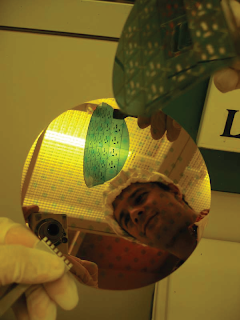

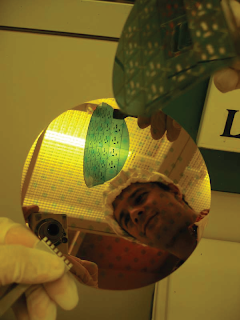

All mainstream semiconductor integrated-circuit processes start with a thin slice of silicon, known as a substrate or wafer. This wafer is circular and ranges from 4 to 18 inches in diameter and is approximately 1 mm thick (hence its name). Each wafer is cut from a single crystal of the element silicon and polished to its final thickness with atomic smoothness (Fig. TF7-1). Most circuit designs (like your processor) fit into a few square centimeters of silicon area; each self-contained area is known as a die. After fabrication, the wafer is cut to produce independent, rectangular dies often known as chips, which are then packaged to produce the final component you buy at the store.

Figure TF7-1: A single 4-inch silicon wafer. Note the

wafer’s mirror-like surface. (Courtesy of Veljko Milanovic

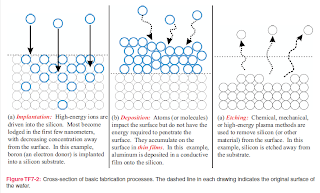

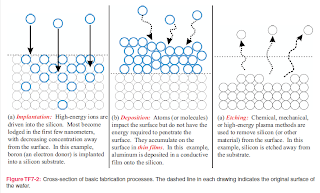

A specific sequence or process of chemical and mechanical modifications is performed on certain areas of the wafer. Although complex processes employ a variety of techniques, a basic IC process will employ one of the following three modifications to the wafer:

• Implantation: Atoms or molecules are added to the silicon wafer, changing its electronic properties (Fig.TF7-2(a)).

• Deposition: Materials such as metals, insulators, or semiconductors are added in thin layers (like painting) onto the wafer (Fig. TF7-2(b)).

• Etching: Material is removed from the wafer through chemical reactions or mechanical motion (Fig. TF7-2(c)).

Lithography

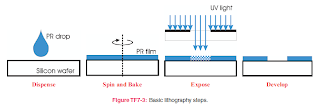

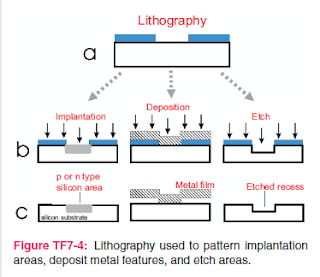

When building a multi-component IC, we need to perform different modifications to differents areas of the wafer. We may want to etch some areas and add metal to others, for example. The method by which we define which areas will be modified is known as lithography.

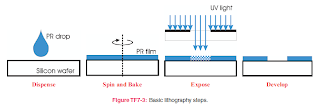

Lithography has evolved much over the last 40 years and will continue to do so. Modern lithography employs all of the basic principles described below, but uses complex computation, specialized materials, and optical devices to achieve the very high resolutions required to reach modern feature sizes. At its heart, lithography is simply a stencil process. In an old-fashioned stencil process, when a plastic sheet with cut-out letters or numbers is laid on a flat surface and painted, only the cutout areas would be painted. Once the stencil is removed, the design left behind consists of only the painted areas with clean edges and a uniform surface. With that in mind, consider Fig. TF7-3. Given a flat wafer, we first apply a thin coating of liquid polymer known as photoresist (PR). This layer usually is several hundred nanometers thick and is applied by placing a drop in the center of the wafer and then spinning the wafer very fast (1000 to 5000 rpm) so that the drop spreads out evenly over the surface. Once coated, the PR is heated (usually between 60 to 100◦C) in a process known as baking; this allows the PR to solidify

slightly to a plastic-like consistency. Once baked and when exposed to ultraviolet (UV) light, the bonds that hold the PR molecules together are “chopped” up; this makes it easy to wash away the UV-exposed areas (some varieties of PR behave in exactly the opposite manner: UV light makes the PR very strong or cross-linked, but we will ignore that technique here). In lithography, UV light is focused through a glass plate with patterns on it; this is known as exposure.

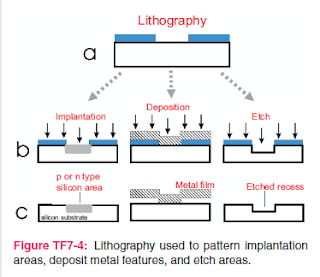

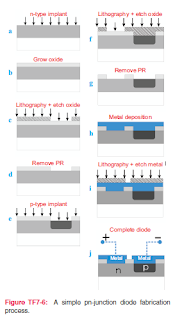

These patterns act as a “light stencil” for the PR.Wherever UV light hits the PR, that area subsequently can be washed away in a process called development. After development, the PR film remains behind with holes in certain areas. How is this helpful? Let’s look at how the modifications presented earlier can be masked with PR to produce patterned effects (Fig. TF7-4). In each case, we first use lithography to pattern areas onto the wafer (Fig. TF7-4(a)) then we perform one of our three processes (Fig. TF7-4(b)), and finally, we use a strong solvent such as acetone (nail polish remover) to completely wash away the PR (Fig. TF7-4(c)). The PR allows us to implant, deposit, or etch only in defined areas.

Fabricating a Diode

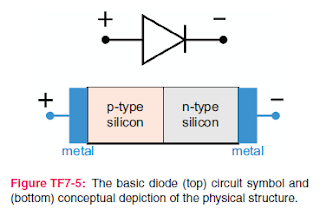

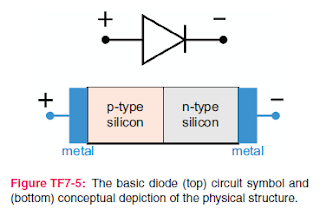

In Section 2-7, we discussed the functional performance of the diode as a circuit component. Here, we will examine briefly how a diode is fabricated. Similar but more complex multi-step processes are used to make transistors and integrated circuits. Conceptually, the simplest diode is made from two slabs of silicon—each implanted with different atoms—pressed together such that they share a boundary (Fig. TF7-5). The n and p areas are pieces of silicon that

have been implanted with atoms (known as impurities) that increase or decrease the number of electrons capable of flowing freely through the silicon. This changes the semiconducting properties of the silicon and creates an electrically active boundary (called a junction) between the n and the p areas of silicon. If both the n and p pieces of silicon are connected to metal wires, this two-terminal device exhibits the diode i–v curve shown in Fig. 2-35(c).

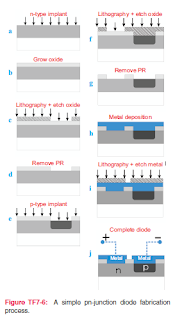

Figure TF7-6 shows the process for making a single diode. Only one step needs further definition: oxidation. During oxidation, the silicon wafer is heated to > 1000◦C in an oxygen atmosphere. At this temperature, the oxygen atoms and the silicon react and form a layer of SiO2 on the surface (this layer is often called an oxide layer). SiO2 is a type of glass and is used as an insulator.

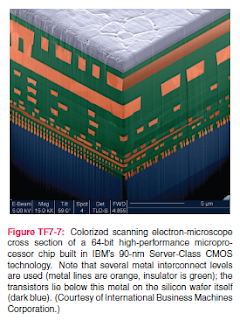

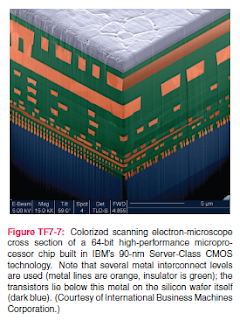

Wires are made by depositing metal layers on top of the device; these are called interconnects. Modern ICs have 6 to 7 such interconnect layers (Fig. TF7-7). These layers are used to make electrical connections between all of the various components in the IC in the same way that macroscopic wires are used to link components on a breadboard.

Adriana Gabriela Trujillo

C.I.17863740

EES

SECC. 02